MichaelSee

n00b

- Joined

- Jan 7, 2024

- Messages

- 2

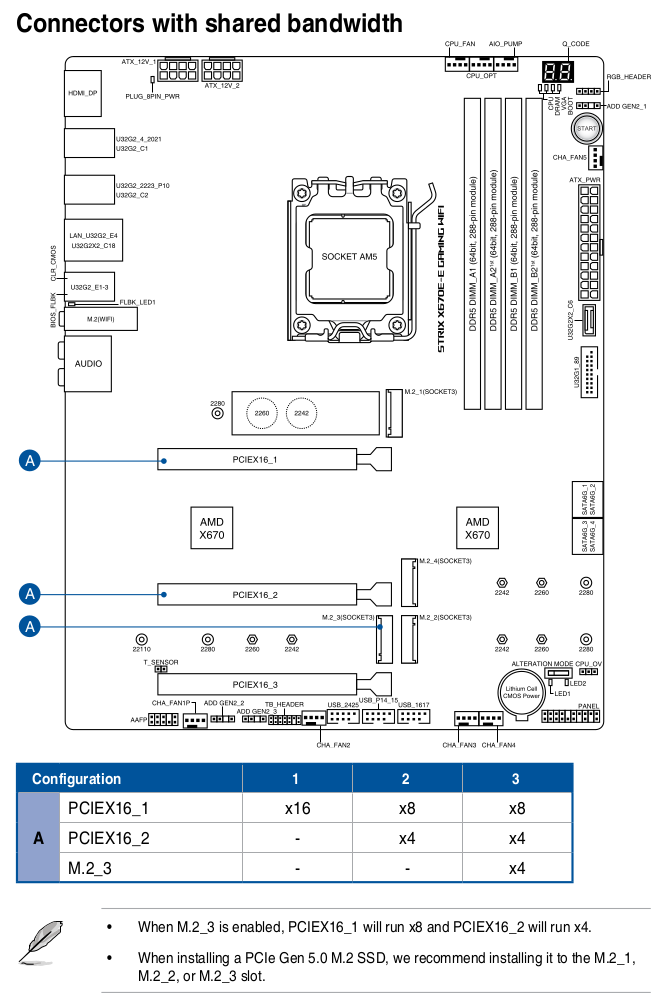

Hi, I have a Asus Strix X670E-E motherboard recently and intend to install few cards that uses all the PCIE slots. I understand the PCIE slots can be configured as either x16/-/x4 (total 20 lanes and PCIEX16_2 disabled), x8/x4/x4 (total 16 lanes and all slots available) or x4/x4/x4/x4 for PCIEX16_1 and x4 for PCIEX16_3 (total 20 lanes and PCIEX16_2 will be disabled). My question is why are the 4 PCIE lanes missing when configuring as x8/x4/x4 and where did they go or reserved for?

Asus launched the RTX4060ti with m.2 slot recently, wouldn't it make sense to configure the BIOS bifurcation to be x8/x4 for PCIEX16_1 and still leave x4 for PCIEX16_2 and x4 for PCIEX16_3 (which is always available due to wiring directly to chipset)? I tried the latest BIOS 1807 that supports the "GPU with m.2" option for PCIEX16_1 but noticed the PCIEX16_2 is still disabled.

P.S. I am using 7950X and 64GB DDR5.

Asus launched the RTX4060ti with m.2 slot recently, wouldn't it make sense to configure the BIOS bifurcation to be x8/x4 for PCIEX16_1 and still leave x4 for PCIEX16_2 and x4 for PCIEX16_3 (which is always available due to wiring directly to chipset)? I tried the latest BIOS 1807 that supports the "GPU with m.2" option for PCIEX16_1 but noticed the PCIEX16_2 is still disabled.

P.S. I am using 7950X and 64GB DDR5.

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)